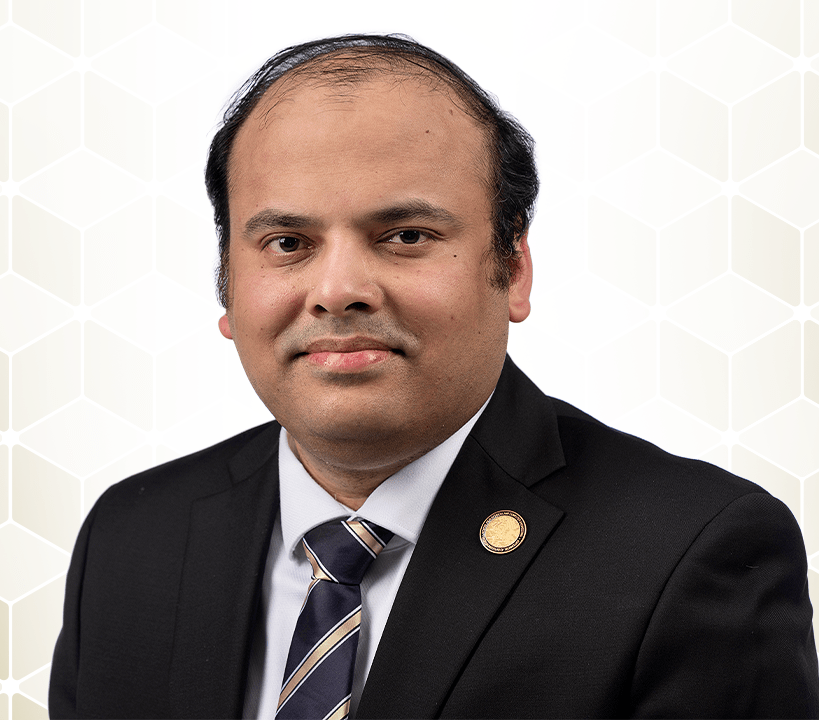

David Anderson

David V. Anderson received the B.S and M.S. degrees from Brigham Young University and the Ph.D. degree from Georgia Institute of Technology (Georgia Tech) in 1993, 1994, and 1999, respectively. He is currently a professor in the School of Electrical and Computer Engineering at Georgia Tech. Anderson's research interests include audio and psycho-acoustics, machine learning and signal processing in the context of human auditory characteristics, and the real-time application of such techniques. His research has included the development of a digital hearing aid algorithm that has now been made into a successful commercial product. Anderson was awarded the National Science Foundation CAREER Award for excellence as a young educator and researcher in 2004 and the Presidential Early Career Award for Scientists and Engineers in the same year. He has over 150 technical publications and 8 patents/patents pending. Anderson is a senior member of the IEEE, and a member the Acoustical Society of America, and Tau Beta Pi. He has been actively involved in the

Audio and Psycho-AcousticsBio-DevicesDigital Signal ProcessingLow-Power Analog/Digital/Mixed-Mode Integrated Circuits