Lim and Team Win 2022 Transactions on Computer-Aided Design Best Paper Award

Jun 02, 2022 — Atlanta, GA

ECE Professor Sung-Kyu Lim

Professor Sung Kyu Lim and his research team have won the 2022 Donald O. Pederson Best Paper Award for their paper “Compact-2D: A Physical Design Methodology to Build Two-Tier Gate-Level 3D ICs.” The prestigious award recognizes the best paper published in IEEE’s Transactions on Computer-Aided Design of Integrated Circuits and Systems (IEEE TCAD), the flagship journal of the IEEE Council on Electronic Design Automation (CEDA).

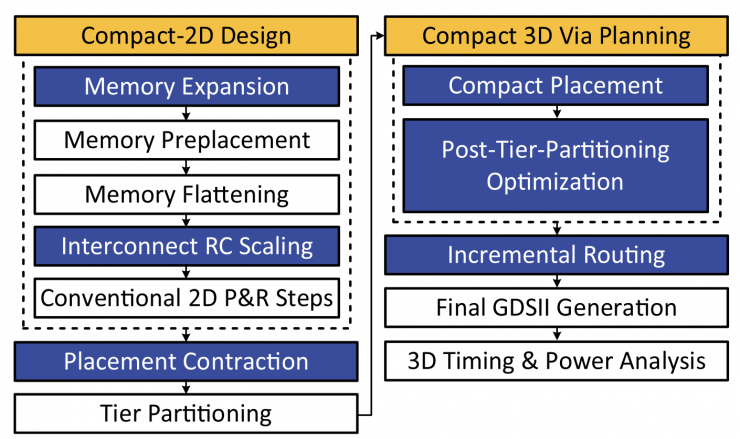

The paper presents a physical design tool named Compact-2D that automatically builds high-density and commercial-quality monolithic three-dimensional integrated circuits (3D ICs). Compact-2D offers first-of-its-kind algorithms and methodologies in partitioning, floorplanning, placement, routing, and timing closure, all targeting 3D ICs under stringent power, performance, and area optimization goals.

The pioneering design leverages the commercial tools readily available for the conventional 2D ICs and extends their capabilities while adding key missing tools to produce 3D IC designs. These extensions include new and better algorithms for physical design automation that simultaneously optimize x, y, and z-dimensions in the design space. With Compact-2D, the team produced 3D IC designs that outperform commercial-quality 2D IC designs for the first time and paved the way for widescale 3D IC proliferation.

Lim, Motorola Solutions Foundation Professor in the Georgia Tech School of Electrical and Computer Engineer (ECE), co-wrote the paper with Bon Woong Ku (former ECE Ph.D. student currently at Synopsys) and Kyungwook Chang (former ECE Ph.D. student currently teaching at Sungkyunkwan University).

The award, sponsored by the IEEE Council on Electronic Design Automation (CEDA), is based on the overall quality, the originality, the level of contribution, the subject matter, and the timeliness of the research. It will be presented to the Georgia Tech team at this year’s Design Automation Conference (DAC) taking place in July 10-14 in San Francisco.

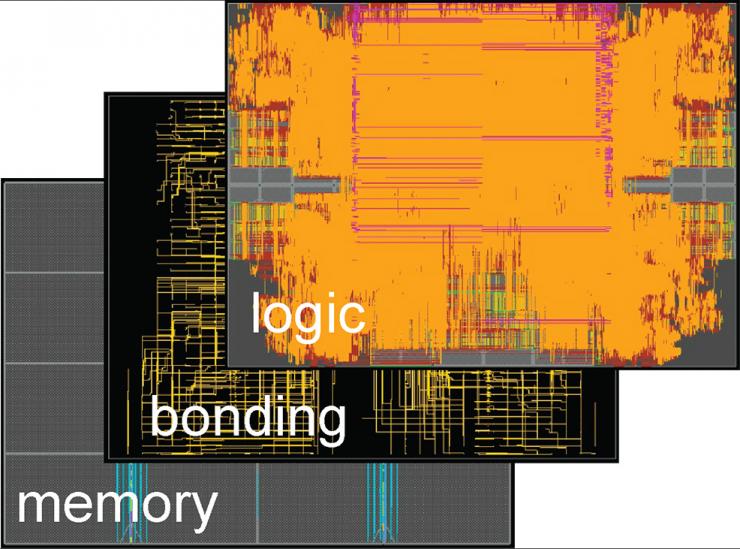

2-Tier Logic-on-Memory 3D IC Physical Design obtained with Compact-2D

Design Flow of Compact-2D for Monolithic 3D ICs.

Dan Watson

dwatson@ece.gatech.edu