Georgia Tech Researchers Develop Wireless Implantable Vascular Monitoring System

May 12, 2022 — Atlanta, GA

Woon-Hong Yeo and his research team have developed a new wireless, electronic vascular monitoring system - a smart stent.

Vascular diseases are public enemy number one: the leading killers worldwide, accounting for nearly a third of all human deaths on the planet.

Continuous monitoring of hemodynamics – blood flow through the vascular system – can improve treatments and patient outcomes. But deadly conditions like hypertension and atherosclerosis occur in long and twisting vascular system with arteries of varying diameter and curvature, and existing clinical devices are limited by their bulk, rigidity, and utility.

Georgia Institute of Technology researcher Woon-Hong Yeo and his collaborators are trying to improve the odds for patients with development of an implantable soft electronic monitoring system. Their new device, consisting of a smart stent and printed soft sensors, is capable of wireless real-time monitoring of hemodynamics without batteries or circuits.

“This electronic system is designed to wirelessly deliver hemodynamic data, including arterial pressure, pulse, and flow, to an external data acquisition system, and it is super small and thin, which is why we can use a catheter to deliver it, anywhere inside the body,” said Yeo, whose team released its study this week in the journal Science Advances.

Yeo added, smiling, “It’s like a stent with multiple tricks up its sleeve.”

For example, when this device is installed in a patient with atherosclerosis, in addition to expanding and preventing the artery from narrowing, like a traditional stent, restoring normal blood flow, it will also provide a constant flow of data.

“Now, once you have deployed a stent, you’re not sure if the problem was resolved and patients may come back with the same issue,” Yeo said. “It can be a defect of the stent, or an issue with stent deployment, or perhaps a problem with the patient’s blood flow.”

And the current standard way to monitor all of that is with an angiogram. That can be expensive and in rare instances, particularly with patients also struggling with diabetes, the dyes and radiation used in angiogram imaging can cause cancer. Yeo’s system seeks to circumvent the need for an angiogram or other imaging requirements.

His wireless smart stent platform, integrated with soft sensors, is operated by inductive coupling to offer wireless real-time monitoring that can detect a wide range of vascular conditions. Inductive coupling uses magnetic fields for wireless energy transfer. It’s similar to what’s happening when you use a wireless charger for your phone, smartwatch, or other devices – they are gaining energy from the magnetic field created by the charger.

“Basically, you can put this sensor system anywhere inside the body,” Yeo explained. “The other thing about this technology platform is, in addition to being an implantable sensor system, it can be used as a wearable system. Think about a smartwatch and how much of its bulk is taken up by circuits or batteries. If you remove all of that, you have a device that is thinner than a typical Band-Aid, an almost invisible health monitor that you can wear anywhere.”

That’s the long-range goal, anyway. So far, they’ve tested their wireless implantable system on animal models. However, there is still plenty of work to do. And Yeo also has the backing of the National Science Foundation to advance the technology. He recently received a 3-year, $400,000 grant from NSF focused on his printed nanomembrane sensors and bioelectronics for wireless and continuous monitoring of vascular health.

“We believe that the mechanical, material, and electrical design principles we develop, and the engineering and biosensing framework that results from this work, will advance the field of implantable electronics and biomedical systems,” Yeo said. “And the insights and knowledge we gain will be applicable for other physiological processes and challenges in biomedical science and engineering.”

CITATION: Robert Herbert, Hyo-Ryoung Lim, Bruno Rigo, Woon-Hong Yeo. "Fully implantable wireless batteryless vascular electronics with printed soft sensors for multiplex sensing of hemodynamics." Science Advances (May 2022)

COMPETING INTERESTS: Hyo-Ryoung and Yeo are the inventors for a pending U.S. patent application related to the work described here. The authors declare that they have no other competing interests.

FUNDING: American Heart Association (grant 19IPLOI34760577), National Institutes of Health (NIH R03EB028928).

This smart stent can continuously monitor arterial pressure, pulse, and flow.

Center for Advanced Electronics through Machine Learning Receives Phase II Funding from The National Science Foundation

May 09, 2022 — Atlanta, GA

Madhavan Swaminathan

As the global demand for microelectronics continues to surge, the mission of the Center for Advanced Electronics through Machine Learning (CAEML) to “apply machine learning to the design of optimized microelectronic circuits and systems” has become even more crucial. As part of Phase I funding from the National Science Foundation (NSF), CAEML researchers and students worked closely with industry partners to develop models and design tools to enable efficient and reliable fabrication of microelectronic systems while protecting intellectual property. With the new Phase II funding, this effort is expected to grow significantly through increased interest and partnership from the semiconductor industry.

“Design space exploration and optimization have had limited success in the past due to slow simulators,” said Madhavan Swaminathan, CAEML site director at Georgia Tech. “In Phase I we have repeatedly shown that machine learning based methods can significantly improve computational time and enhance productivity. These advantages have been quantified by several CAEML industry partners through deployment of these techniques into their workflow.”

During phase I, the team published more than 70 papers, delivered 20 webinars, and received 11 awards or award nominations for their work with the Center. In addition, 12 students who participated in CAEML’s Phase I research have been hired by industry partners.

CAEML is part of the NSF’s Industry-University Cooperative Research Center (IUCRC) program and includes faculty from Georgia Tech, the University of Illinois Urbana-Champaign (UIUC), and North Carolina State University (NCSU). Phase II is a five-year award and begins August 1, 2022.

“In Phase II we plan to address the end-to-end system design challenges by developing solutions to five technical challenges posed by industry using machine learning in the areas of analog circuit design, signal integrity, hardware security, reliability, and data access,” said Swaminathan, who also serves as the John Pippin Chair in Microsystems Packaging and Electromagnetics and Director of the Packaging Research Center at Georgia Tech.

In addition to Swaminathan, the leadership team for CAEML consists of Elyse Rosenbaum, Melvin and Anne Louise Hassebrock Professor in Electrical and Computer Engineering, UIUC and Paul Franzon, Cirrus Logic Distinguished Professor of Electrical and Computer Engineering and Director of Graduate Programs in Electrical and Computer Engineering at NCSU.

Read the full press release.

NNCI Webinar: Societal and Ethical Implications

Science Policy Around the World in 2022: Innovations and Uncertainties in the Global Knowledge System

During the last two years, we have been living in a foreign world. Most activities have been altered in response to the Covid-19 pandemic, shifting our ways of living and interaction with others. Even the mechanisms through which we gather knowledge have changed.

Paul Joseph Awarded Fulbright Specialist Grant to India

Apr 29, 2022 — Atlanta, GA

Paul Joseph, a principal research scientist in the Institute for Electronics and Nanotechnology (IEN) at Georgia Tech, has received a Fulbright Specialist Award to India from the Fulbright Foreign Scholarship Board. Joseph will spend two weeks at the Indian Institute of Information technology (IIIT) this summer helping to expand the nanotechnology curriculum and assisting with faculty and student skill development at IIIT.

Joseph will bring more than 25 years of research and teaching experience in an academic setting to his host institution. In his current role at IEN, Joseph serves as the director of external user programs for the Southeastern Nanotechnology Infrastructure Corridor (SENIC) and manages and facilitates external research projects for academic and industry users of the NSF-funded National Nanotechnology Coordinated Infrastructure (NNCI) shared user labs. He also teaches a short course in soft lithography for microfluidics, coordinates the NanoFANS Forum, and conducts collaborative research with other faculty colleagues at Georgia Tech in micro- and nanotechnology.

Recently, Joseph received his MBA specializing in technology innovation and commercialization from the Scheller College of Business at Georgia Tech. He was also elected as IEN’s representative to the Georgia Tech Interdisciplinary Research Faculty Advisory Council. He plans to share his knowledge, specifically in nano- and microelectronics, fabrication methodologies, and nanomaterial characterization, through lectures and daily mentoring hours for IIIT students.

“My lectures on important topics will expose the students to the benefits of nanotechnology and will help widen their knowledge and skills in the field,” explained Joseph. “I hope this will help them explore career opportunities in nanoscale science and technology, which are expanding rapidly due to their increasing impact on many aspects of our daily lives.

“Nanotechnology offers the potential for tremendous advancements in the development of commercial products in electronics, energy, healthcare, the environment, and food, just to name a few,” he added. “It is one of the most powerful emerging and enabling technologies in the world, and Indian industries have started realizing the commercial viability of nanotechnology quite recently. Because of this, it is one of the hottest career options available to Indian engineering/science graduates.”

Joseph also hopes to create lasting relationships with the faculty at IIIT that will last beyond this visit. He plans to conduct group lectures and discussion sessions with faculty members on student engagement, course design for transformative education, best practices to gain research funding, how to design and lead a collaborative research team, and technology commercialization assessments for potential start-ups.

Beyond the benefits to Georgia Tech and IIIT, Joseph, who is a native of India, expects to benefit personally as well. “I see this as a great opportunity to participate in cross-cultural professional development, gain international exposure, and use my many years of experience in a new and a creative way,” he said. “It is a great opportunity to share my expertise and life experiences with overseas counterparts and learn about my field of research from a new perspective. I am very excited for this opportunity to give back to the country where I was born.”

IEN’s NanoFANS Forum Celebrates 25th Symposium

Apr 29, 2022 — Atlanta, GA

The NanoFANS (Focusing on Advanced Nanobio Systems) Forum is a semiannual symposium supported by the Institute for Electronics and Nanotechnology (IEN) at Georgia Tech that began in 2008. It features topics at the intersection of the life sciences and nanotechnology, and connects the medical, life sciences, biology, nanotechnology, and engineering communities. The goal of the NanoFANS Forum is to engage researchers in the biomedical and life sciences areas and to educate them on the benefits of micro-/nanotechnology and how it can advance their research.

Since the beginning, NanoFANS has been attended by more than 2,500 participants, both on- and off-campus, from academia, industry, and government organizations. To date, IEN has hosted 24 events and featured about 80 Georgia Tech / Emory faculty (and one off-campus faculty from Clemson).

The 25th NanoFANS forum is on Tuesday, May 24th, and will focus on “Micro- and Nanotechnology Commercialization: Opportunities and Challenges.” Technology commercialization is the process of transitioning technologies from the research lab to the marketplace, and it complements the process of publishing research findings. Innovations in micro- and nanotechnology are revolutionizing manufacturing and production and creating new materials and products through novel processes for commercial applications. In many cases, there is also a significant benefit to society.

IEN’s 25th NanoFANS forum will explore the opportunities and challenges of commercializing innovations in micro- / nanotechnology in the bio- space. Speakers will include Professor Todd Sulchek from the Woodruff School of Mechanical Engineering at Georgia Tech; Professor Farrokh Ayazi from the School of Electrical and Computer Engineer at Georgia Tech, Regents Professor Mark Prausnitz from the School of Chemical and Biomolecular Engineering at Georgia Tech, and Mason Chilmonczyk, CEO of Andson Biotech. They will discuss their innovations and commercialization experience as founders and co-founders of their start-ups.

Please register for the NanoFANS Forum by May 20, 2022. Lunch will be provided

After the talks, an optional tour of the state-of-the-art IEN Cleanrooms and labs will be available for interested participants. Please let us know if you are interested in taking a tour.

For more information on the NanoFANS Forum, please contact:

Paul J. Joseph, Ph.D., MBA

Principal Research Scientist

Georgia Tech Institute for Electronics and Nanotechnology

Spring 2022 IEN Microfabrication Short Course

The Institute for Electronics and Nanotechnology (IEN) at Georgia Tech will offer a short course on microfabrication from May 25th - 27th, 2022. This intensive three-day short course combines classroom lectures and laboratory based hands-on fabrication in the IEN cleanroom. The goal of the course is to impart a basic understanding of the science and technology of microfabrication processes as used in academia and industry.

PRC Distinguished Lecture Seminar | Directions in III-N Devices for Wireless Communications and Beyond

Featuring Professor Patrick Fay, Department of Electrical Engineering, University of Notre Dame

Bio LaunchPad Symposium

"Navigating the Early Stages of Biotech Commercialization"

Featuring:

Daria Mochly-Rosen, Ph.D.

George D. Smith Professor in Translational Medicine

Stanford University

A two-day meeting delivering the basics of biomedical translational and commercialization work though the inspiring story of Daria Mochley-Rosen, Ph.D., founder of Stanford’s SPARK program.

Terahertz Imaging Reveals Hidden Inscription on Early Modern Funerary Cross

Apr 25, 2022 — Atlanta, GA

Georgia Tech professor David Citrin (right) and adjunct professor Alexandre Locquet stand in front of an image of the 16th-century funerary cross used in their study. Credit: Nicolas Jacquet

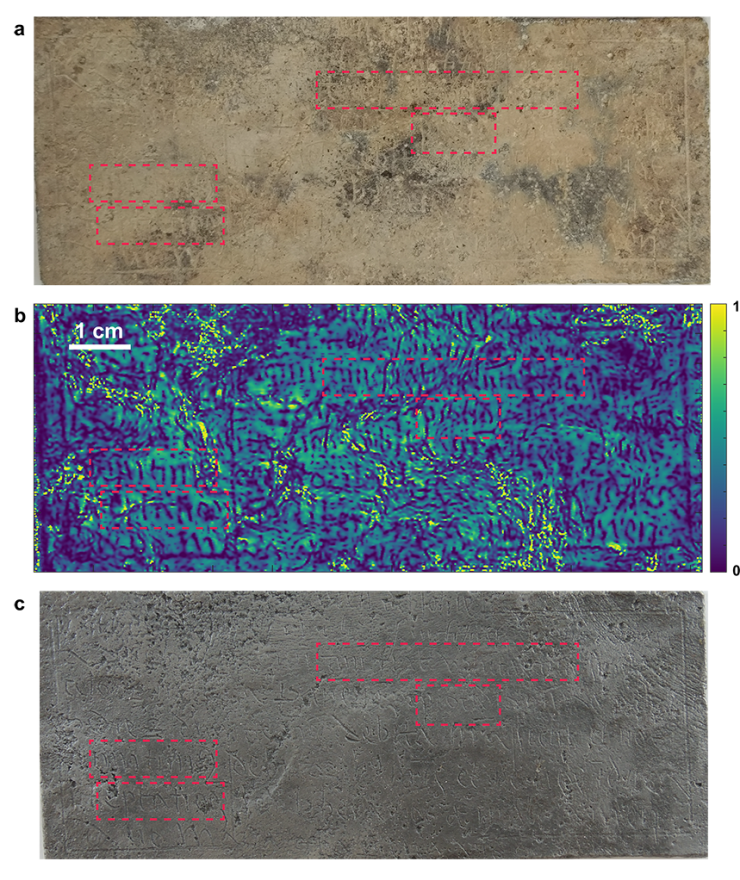

In a multidisciplinary project, researchers at the Georgia Institute of Technology and Georgia Tech-Lorraine used terahertz imaging and signal processing techniques to look beneath the corroded surface of a 16th-century lead funerary cross. Led by David Citrin, a professor in the School of Electrical and Computer Engineering (ECE), the effort brought together imaging scientists, a chemist specializing in archaeological objects, and an art historian to reveal a message that had been obscured by time: an inscription of the Lord’s Prayer.

“Our approach enabled us to read a text that was hidden beneath corrosion, perhaps for hundreds of years,” said Alexandre Locquet, an adjunct professor in ECE and researcher at Georgia Tech-CNRS IRL 2958, a joint international research laboratory at the Georgia Tech-Lorraine campus in Metz, France. “Clearly, approaches that access such information without damaging the object are of great interest to archaeologists.”

The study was reported March 2 in the journal Scientific Reports.

The cross, cut from a sheet of lead, was found in a burial plot at an abbey in Remiremont, France — a couple hours drive from the Georgia Tech-Lorraine campus. Known as a croix d’absolution, it is a type of funerary cross that dates to the Middle Ages and has been found at sites in France, Germany, and England.

“This type of cross typically bears inscriptions of prayers or information about the deceased,” said Aurélien Vacheret, director of the Musée Charles-de-Bruyères in Remiremont and co-author on the study. “It is thought their purpose was to seek a person’s absolution from sin, facilitating their passage to heaven.”

The museum loaned the cross to Citrin’s lab in hopes that the team could use imaging techniques to make the invisible visible. Citrin and his group specialize in non-destructive evaluation and develop techniques that allow for detailed examination of an object’s hidden layers without changing or damaging its original form. Although their work often has industrial applications, such as detecting damage to airplane fuselages, the group embraced the opportunity to inspect the cross – a chance to further explore their technology’s applications for archaeological purposes.

Peeking Beneath the Veil of Corrosion

The team used a commercial terahertz scanner to examine the cross every 500 microns (about every half a millimeter) across the object. First, the scanner sent short pulses of terahertz electromagnetic radiation — a form of light that travels on tiny wavelengths — over each section of the cross. Some waves bounced back from the layer of corrosion, while others penetrated through the corrosion, reflecting from the actual surface of the lead cross. This produced two distinct echoes of the same original pulse.

Next, the team used an algorithm to process the time delay between the two echoes into a signal with two peaks. This data revealed how thick the corrosion was in each scanned point. The measurements of the light beams that reflected from the underlying metal were then collected to form images of the lead surface below the corrosion.

Interdisciplinary Insights

Although crucial data was gathered during the scanning process, the raw images were too noisy and jumbled and the inscription remained illegible at the time. But Junliang Dong, then a Ph.D. student in Citrin’s lab, had the insight to process the images in a special way to eliminate the noise. By subtracting and piecing together parts of the images acquired in different frequencies, Dong was able to restore and enhance the images. What was left was a surprisingly readable image containing the text.

Using the processed images, Vacheret was able to identify multiple Latin words and phrases. He determined they were all part of the Pater Noster, commonly known as the Our Father or the Lord’s Prayer.

The team also worked with a conservationist to chemically reverse the corrosion on the cross, confirming the Pater Noster inscription. Comparing their images to the clean cross, the team found their images had revealed parts of the inscription not observable on the original cross. By uncovering additional aspects of the inscriptions that were previously undocumented, their work was able to offer deeper understanding of the cross and further insight into 16th-century Christianity in Lorraine, France.

“In this case, we were able to check our work afterwards, but not all lead objects can be treated this way,” Citrin said. “Some objects are large, some must remain in situ, and some are just too delicate. We hope our work opens up the study of other lead objects that might also yield secrets lying underneath corrosion.”

Citrin’s group has also used terahertz imaging to look beneath the surface of 17th-century paintings, elucidating paint layer structure and providing insights into techniques of master painters. They are currently investigating surface coatings on ancient Roman ceramics.

The cross project illustrates that success requires more than just accurate measurement, but also careful data processing and collaboration between researchers from disparate fields. The team’s approach opens new perspectives for terahertz imaging analysis and could produce great boosts for the fields of digital acquisitions and documentation, as well as character recognition, extraction, and classification.

“Despite three decades of intense development, terahertz imaging is still a rapidly developing field,” said Locquet. “While others focus on developing the hardware, our efforts concentrate on making the most of the data that is measured.”

Citation: Junliang Dong, Ana Ribeiro, Aurélien Vacheret, Alexandre Locquet, and D. S. Citrin, “Revealing inscriptions obscured by time on an early-modern lead funerary cross using terahertz multispectral imaging,” Scientific Reports (March 2, 2022).

DOI: https://doi.org/10.1038/s41598-022-06982-2

Funding: This work was funded by the Fonds Européen de Développement Régional (FEDER) from the Conseil Régional du Grand Est, as well as the Institut Carnot ARTS.

About Georgia Tech

The Georgia Institute of Technology, or Georgia Tech, is a top 10 public research university developing leaders who advance technology and improve the human condition. The Institute offers business, computing, design, engineering, liberal arts, and sciences degrees. Its nearly 44,000 students, representing 50 states and 149 countries, study at the main campus in Atlanta, at campuses in France and China, and through distance and online learning. As a leading technological university, Georgia Tech is an engine of economic development for Georgia, the Southeast, and the nation, conducting more than $1 billion in research annually for government, industry, and society.

Comparison of the inscription on (a) the original cross before corrosion removal, (b) the final terahertz image after post-processing, and (c) the cross after corrosion removal.

Catherine Barzler, Senior Research Writer/Editor

Georgia Tech Quantum Alliance Workshop

Program

9:00 a.m. - 9:15 a.m. - Welcome Martin Mourigal and Alexa Harter

9:15 a.m. - 9:40 a.m. - Colin Parker (Physics) Invited Talk

9:40 a.m. - 10:05 a.m. - Ali Adibi (ECE) Invited Talk

10:05 a.m. - 10:30 a.m. - Coffee Break

10:30 a.m. - 11:30 a.m. - Student Session I